APPLICATION NOTE

HD-000153-AN-3-Minimizing PCB parasitic effects

MINIMISING PCB PARASITIC EFFECTS WITH OPTIMUM LAYOUT OF THE GATE DRIVER LOOP

Introduction - Review of Fundamentals - Gate Driver Circuit - Conclusions - Disclaimer -

Introduction

In order to reduce circuit size and increase density, the switching frequency of high-power converters is increasing all the time. It is not uncommon to see switching frequencies above 500kHz and even beyond 1MHz in higher power converter applications. This increase is further supported by the introduction of high-power, low RDS_ON and low gate capacitance MOS and GaN FETs.

To facilitate this high frequency operation a new range of FET drivers such as the HEY1011, is required to maximize the effectiveness of these FET switches.

Faster switching edges both in the gate drive loop and the commutation loop are a continuous design challenge. The effects of PCB parasitic parameters can play a significant role in circuit operation. Here we focus on optimisation of the gate drive loop for minimum parasitics using the Heyday HEY1011 isolated gate driver.

The PCB tracking and layout is a fundamental part of the operation of an electronic circuit. The PCB tracks themselves introduce inductances and capacitances into the circuit which can often be over looked. In power switching circuits, these parasitic components can introduce voltage and current ringing on circuit nodes which can greatly inhibit the performance of the circuit and introduce undesired effects such as poor circuit operation and increased EMI.

A solution is often to add, after the fact, components such as snubbers and filters. A better approach is to eliminate or minimise the effects through good PCB layout practices.

This paper discusses some of these effects and shows how to minimise PCB parasitic effects with optimum layout of the gate driver loop.

Review of fundamentals

In order to understand the effects of PCB parasitic inductances and capacitances, it may be useful to review some fundamental concepts.

Inductance

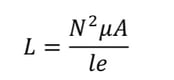

Estimating the inductance of a PCB track is very difficult and made even more so given the high frequency effects on current flow such as eddy currents and skin effect. However, a review of a fundamental formula for inductance shows how it can be minimised.

where N = number of turns, μ = permeability, le = magnetic path length, A = cross section area

For an electronic circuit, the number of turns, N, is normally equal to one; that is the go and return path of the current in question. The cross-section area, A, is the area encompassed by this current and is one parameter we can control through good PCB layout practices.

Figure 1: Reducing cross sectional loop area reduces inductance

Capacitance

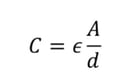

As with the inductance of PCB tracks, calculating the capacitance between two areas of PCB copper is very difficult. Again, looking at a fundamental formula for the capacitance between two conductors can show what parameters we can control with the PCB design.

where ε = permittivity, A = common area of the plates, d = distance between the plates

The permittivity is a function of the PCB material; normally FR4 with a permittivity of 4.7. ‘d’ is the distance between the overlapping copper as is defined by the PCB stack up. ‘A’ is the common area or area of overlap of the conductors.

It is normal practice to use wide and large areas of copper, such as ground planes, to reduce trace impedance. However, it should be remembered that such large areas can add significant capacitance to a sensitive circuit node and the effect of this capacitance must be borne in mind.

Vias

Again, calculating the inductance of a PCB via is very difficult. A good rule of thumb is 1nH per via. This needs to be borne in mind when deciding if it is better to use vias to an internal layer or keep the go and returns traces on the same layer.

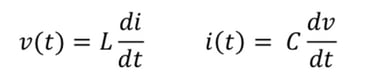

Voltage and current formulae

Looking at the fundamental formulae for voltages and currents in capacitors and inductances, it can be seen that a critical factor is the ‘rate of change’ of the voltage or current rather than the amplitude of the changing voltage or current itself.

That is, in the case of an inductor, a rapidly changing current, even if that current is small in amplitude, can result in a large voltage drop across the inductor (or PCB trace). A current of 10mA switching in 1ns will result in the same voltage drop as a current of 10A switching in 1µs.

Similarly, for capacitors, a rapidly changing voltage across the capacitor can result in a very large current. This current must always return to its source and if not managed correctly with good PCB layout can result in unwanted EMI interference.

With power converter circuits, the trend towards higher powers and higher switching frequencies can mean switching 10s or 100s of volts or amps with rise and fall times of sub 10ns. With these levels of switching speeds, every nano-henry or pico-farad can have a significant effect on circuit performance.

Gate driver circuit

The HEY1011 is a driver module for driving GaN FETs, https://www.heyday-ic.com/gan-drivers. The HEY2011 driver range are excellent for driving MOS FET switches, https://www.heyday-ic.com/mos-drivers.

Heyday drivers have the unique advantage in that they require the minimum of external components, particularly on the output side, which is the most critical from a PCB layout point of view. The Heyday drivers do not require a separate isolated or bootstrap diode – all of that functionality is included in the drivers using our unique Power-thru® technology.

The pinout of the device has been carefully designed for ease of PCB layout and optimum performance.

Good quality decoupling capacitors should be used for decoupling the primary, VDRV, and secondary, CSEC, voltages. And again, the HEY1011 LGA pinout has been designed for the optimimum positioning of these capacitors.

The OUTPU (FET drive on) and OUTPD (FET drive off) can be used directly to the FET gate or with series resistors to control the FET rise and fall times. Having these functions separated but adjacent on the module allows for independent control of the turn on and off times without the need for external parallel diode or transistors circuits while still allowing the driver to be as close as possible to the driven FET.

The gate drive current return to the module is through the OUTSS pins and these have been positioned to allow for the minimum loop area for the gate current.

The example PCB layout below shows the HEY1011 used with a GaN Systems GS66516T FET and follows the recommended layout for the GS66516T and the principles described above.

Figure 2 : HEY1011 PCB layout with GaN Systems GS66516T

Conclusions

The ever-increasing switching frequencies of power converters results in faster voltage and current transition edges – higher dv/dt’s and di/dt’s. This puts more emphasis on the PCB layout.

Good PCB layout practices can significantly reduce second order effects such as EMI and can reduce or eliminate the need for circuits such as snubbers or filters required to manage these phenomena.

The Heyday isolated GaN & MOS FET drivers have been designed to make this process easier resulting in more effective gate drive applications.

Disclaimer

Heyday Integrated Circuits (“Heyday”) provides all data in any resource and in any format such as, but not limited to datasheets, reference designs, application notes, web tools and safety information “as is” and with all faults, and disclaims any type of warranties, fitness for a particular purpose or non-infringement of 3rd party intellectual property rights. Any examples described herein are for illustrative purposes only and are intended to provide customers with the latest, accurate, and in-depth documentation regarding Heyday products and their potential applications. These resources are subject to change without notice. Heyday allows you to use these resources only for development of an application that uses the Heyday product(s) described in the resource. Other reproduction and display of these resources is prohibited. Heyday shall have no liability for the consequences of use of the information supplied herein.

Download